Visible to Intel only — GUID: bmh1582102130248

Ixiasoft

Visible to Intel only — GUID: bmh1582102130248

Ixiasoft

4.7. Hardware Test for System Console Control Design Example

- Launch the System Console tool from Intel® Quartus® Prime (Tools > System Debugging Tools > System Console).

- In the TCL Console command prompt, type get_service_paths master to print a list of devices connected to your JTAG chain.

- Open the main.tcl Tcl script located in the System Console directory in any text editor of your choice and locate the following line.

set master_index [expr {$master_list_length - <your offset>}] - Adjust the master_index offset as necessary to reflect your JTAG chain configuration such that the master_index always points to the Intel® Agilex™ device and save the file.

- In the TCL Console command prompt, navigate to the system_console directory (cd system_console) and execute the main.tcl script (source main.tcl). Your TCL Console window should resemble the following figure.

Figure 9. Source main.tcl

- Type start_basic_test at the command prompt to execute the link setup and test procedure.

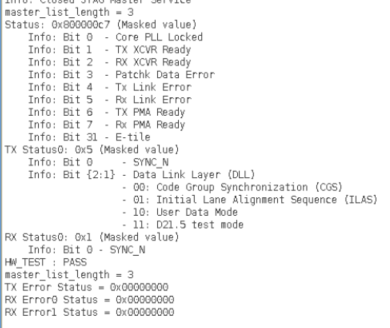

This procedure executes a set of instructions to set up the pattern generator and checker to transmit and check PRBS pattern, configure the JESD204B IP PHY internal serial loopback mode and report link status.The following figure illustrates the expected result from a successful link setup and test.Figure 10. Successful Test in the System Console

- In the event that the test fails due to a lane deskew error, use the rbd_offset procedure (described in the following table) to offset the default RBD setting. Refer to the JESD204B Intel® FPGA IP User Guide for more details on using the RBD offset.

Table 19. Procedures in the main.tcl System Console Script The table describes useful procedures in the main.tcl that may be helpful in debugging. Procedure Values Description get_service_paths {master} Reports all devices that are connected to the JTAG chain. Use this information to set the master index to point to the Intel® Agilex™ device get_master_index N/A Sets the targeted device master index. Use get_service_paths master to determine the offset of the Intel® Agilex™ device in the JTAG chain, and edit the offset in this procedure accordingly. start_basic_test N/A Main procedure that sets up link serial loopback mode, pattern generator and checker test mode, pulses sysref and reports link status reset N/A Global reset force_link_frame_reset {0,1} 0: Deasserts link and frame resets

1: Asserts and holds link and frame resets

Note: Link and frame clock domains should be held in reset while writing to JESD204B IP CSRsloopback {0,1} 0: Disables internal serial loopback

1: Enables internal serial loopback

set_testmode {alt, ramp, prbs} alt: Sets pattern generator and checker to alternate pattern

ramp: Sets pattern generator and checker to ramp pattern

prbs: Sets pattern generator and checker to PRBS pattern

rbd_offset {integer} Adjusts RBD offset value to eliminate RX lane deskew error. sysref N/A Single pulse sysref read_status_pio N/A Reads status PIO registers. PIO status configuration:

Bit 0 — Core PLL locked

Bit 1 — TX transceiver ready

Bit 2 — RX transceiver ready

Bit 3 — Pattern checker mismatch error

Bit 4 — TX link error (use read_err_status procedure to report error description)

Bit 5 — RX link error (use read_err_status procedure to report error description)

read_err_status N/A Reads JESD204B IP error status registers. Refer to the JESD204B IP register maps for detailed description of status registers. clear_err_status N/A Clears JESD204B IP error status registers read_rx_status0 N/A Reads JESD204B IP rx_status0 register. Refer to the JESD204B IP register maps for detailed description of status registers read_tx_status0 N/A Reads JESD204B IP tx_status0 register. Refer to the JESD204B IP register maps for detailed description of status registers. read_rx_syncn_sysref_ctrl N/A Reads JESD204B IP syncn_sysref_ctrl register. Refer to the JESD204B IP register maps for detailed description of status registers wait_seconds {integer} Waits for {integer} seconds wait_minutes {integer} Waits for {integer} minutes det_etile {0,1} 0: Checks if the E-tile transceiver does PMA configuration for internal loopback

1: Checks if the E-tile transceiver does PMA configuration for external loopback

Note: Applicable only for designs using E-tile devices.eval_test N/A Reports link status. Note: Applicable only for designs using L-tile and H-tile devices.eval_test_etile N/A Reports link status. Note: Applicable only for designs using E-tile devices.