Visible to Intel only — GUID: sic1587708466351

Ixiasoft

1.1. Hardware Requirements

1.2. Hardware Setup

1.3. JESD204C Intel® FPGA IP and ADC Hardware Checkout

1.4. JESD204C Intel® FPGA IP and DAC Hardware Checkout

1.5. Document Revision History for AN 916: JESD204C Intel® FPGA IP and ADI AD9081/AD9082 MxFE* Interoperability Report for Intel® Stratix® 10 E-Tile Devices

1.6. Appendix

Visible to Intel only — GUID: sic1587708466351

Ixiasoft

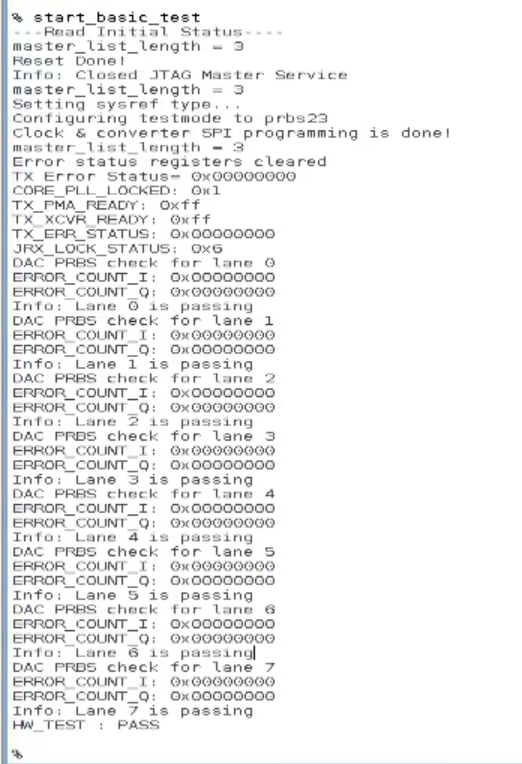

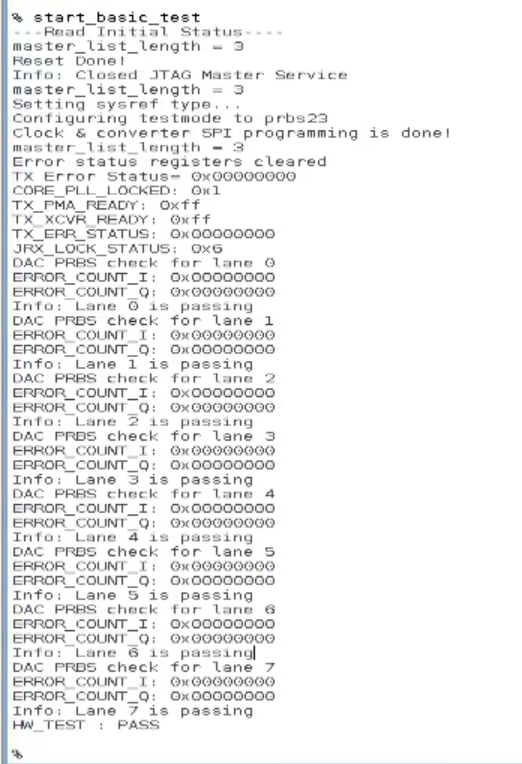

1.4.3. DAC Test Results

The following table shows the results for test cases TXRST.1 and TXTL.1 with subclass 0 and FCLK_MULP = 2.

| Test No. | L | M | F | E | Lane Rate (Mbps) | DAC Rate (Msps) | Link Clock (MHz) | Result |

|---|---|---|---|---|---|---|---|---|

| 1 | 8 | 8 | 2 | 1 | 16000 | 1939.39394 | 121.212121 | PASS |

The following figure shows the Signal Tap waveform of the PRBS pattern data transmitted to FPGA transmitter transport layer.

Figure 7. PRBS Data Pattern Diagram

The following figure shows the result of the pattern checker at output data of DAC transport layer.

Figure 8. DAC PRBS Checker Result