Visible to Intel only — GUID: joc1462997552128

Ixiasoft

Visible to Intel only — GUID: joc1462997552128

Ixiasoft

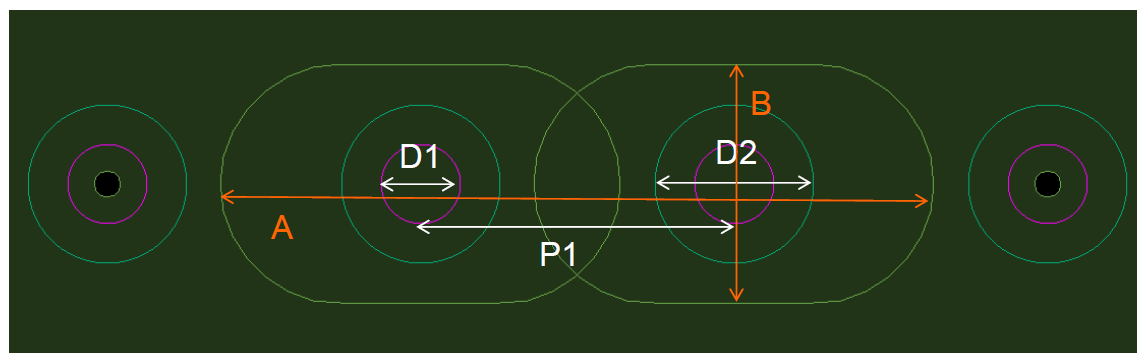

Option 1: Via-In-Pad Topology

Intel recommends using via-in-pad technology for data rates above 15 Gbps. Use via-in-pad when you want to transfer signals from the BGA pad to the inner layers.

D1: Via drill hole diameter: 8 mil (for up to 1:12 stackup aspect ratio) or 10 mil for higher stackup aspect ratios.

D2: Via pad diameter: 18 mil (for up to 1:12 stackup aspect ratio) or 20 mil for higher stackup ratios.

P1: Standard via-to-via pitch: 1 mm.

A: Horizontal anti-pad: 90 mil.

B: Vertical anti-pad: 28 mil (for up to 1:12 aspect stackup ratio) or 30 mil for higher stackup aspect ratios.